[NOTE: The following is the thesis proposal for my Masters Thesis that was completed in December 2017. The full text of the thesis itself has not been included because it is currently undergoing the patent process as of February 2018]

A Class-1 Generation-2 Conforming UHF RFID IC Optimized for CDMA: Designing an Open and Modular UHF RFID IC

Ramsey Doany, Ingram School of Engineering, Texas State University

Student Member, IEEE

Abstract:

With the use of RFID technology becoming more widespread across the landscape of electronics, both large and small scale research into the field is occurring all over the world. However, due to the secret and proprietary nature of RFID tag design, tag manufacturers have effectively limited independent research to a systems level analysis resulting in non-commercial research and development being stuck to theoretical analysis and simulation. A need exists for a totally open RFID system in which the user can modify and test every aspect of the system. The proposed research is to optimize the Slotted ALOHA RFID communication protocol by employing CDMA while conforming to the current Class-1 Generation-2 Standard. To achieve this goal, part of the research will involve designing the research tool itself: a modular FPGA-based RFID IC emulator. In previous work, successful software and hardware simulations of a CDMA-based UHF RFID system was demonstrated but due to prohibitively expensive equipment and little to no cooperation from companies in a highly IP driven industry there was no possibility to design or modify actual UHF RFID tags. As part of the proposed thesis, several CDMA implementations on an RFID IC will be developed, tested, and optimized and an inexpensive framework supporting open RFID IC research will be established. This research will be conducted using HDL simulation and FPGA-Implementation of a CDMA-integrated Slotted ALOHA protocol.

List of Abbreviations:

RFID – Radio Frequency Identification

CDMA – Code Division Multiple Access

TDMA – Time Division Multiple Access

UHF – Ultra High Frequency

FPGA – Field Programmable Gate Array

DSSS – Direct Sequence Spread Spectrum

EPC – Electronic Product Code

EEPROM – Electronically Erasable Programmable Real Only Memory

USRP – Universal Software Radio Peripheral

SDR – Software Defined Radio

-

Introduction

1.1 Background

In a previous R&D project, I worked in a student team tasked with designing an RFID system that used CDMA and DSSS for its multiplexing scheme to enable the ability to read multiple RFID tags simultaneously. Initially, we thought that we would be able to build our own UHF tag but were limited by the equipment available to us. Our second idea was to modify existing RFID tags. This proved impossible not because of a lack of available tools or any laws of physics but because RFID tag manufacturers make their tags non-reconfigurable and were uninterested in granting us access to the devices that they use for research and development. All UHF RFID development kits on the market today are limited to modifying the RFID interrogator but none allow for changes in the RFID tag architecture, multiplexing schemes, data storage protocols, memory allocation, or even tag EPC format. This led our team to be limited in our research to simulation and while we were able to complete a software simulation as well as a hardware simulation to demonstrate our successful research and were even able to publish for our work, we were never able to implement our system into an actual RFID environment. Further reading on the subject makes it clear that the vast majority of non-commercial research has been limited to pen-and-paper mathematics and simulation. While there exist ‘open’ UHF RFID tags (most notably the WISP tags designed by the University of Washington with support from Intel), they are based around microprocessors, thus still limiting their use in RFID IC architecture research and design (and are prohibitively expensive). I am proposing to continue my research in CDMA-based RFID by designing an RFID IC that is optimized for various CDMA implementations. In doing so, the framework for open RFID IC design will be established, enabling new paths for future RFID research.

1.2 Radio Frequency Identification and the Slotted ALOHA Protocol

Radio Frequency Identification (or RFID) is a wireless communication technology that allows for wireless non-line-of-sight inventory tracking and many other applications. An RFID system contains two main components: The RFID Interrogator and the RFID tag. The Interrogator is used to write data to the tag, read data from the tag, and provide power for the tag (if the tag is passive). The Interrogator includes a processor and/or an FPGA and an antenna. The RFID tag contains data and is affixed to a sticker, badge, etc. and contains an IC and an antenna. The RFID tag can either be passive (i.e. no internal power source) or it can be active (i.e. contains an internal power source). The main components of the passive RFID tag’s IC are the analog front end which is used for wireless communication with the interrogator, a random number generator which is used for its multiplexing scheme, EEPROM, and its digital circuitry which acts as a state machine. The passive RFID tag communicates with the interrogator by modifying and reflecting received signals.

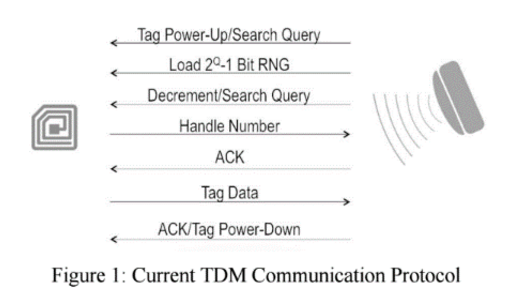

The most widely used passive RFID tag is the Class-1 Generation-2 UHF RFID tag that employs a Framed Slotted ALOHA protocol to communicate with the Interrogator [1]. This protocol allows for multiple RFID tags within a system to be read using time division multiple access. The basic outline of which is as follows:

- The Interrogator powers-up all tags within range

- The Interrogator instructs all tags to load their random number generators (Range = 2Q-1, Q selected by designer)

- The Interrogator transmits decrement command so that all tags decrement their random number by 1

- If no tag reaches 0 after the current decrement command, the Interrogator transmits another decrement command

- Once a tag’s random number reaches 0, it transmits its handle number to the Interrogator

- The interrogator acknowledges the tag

- The tag transmits its data to the Interrogator

- The Interrogator re-acknowledges the tag and instructs it to power down

- The process repeats from step 3 until all tags are read by the interrogator.

This process is visualized in Figure 1 below.

In the case of a collision (i.e. two or more tags generate the same random number), all tags that have not been powered down are instructed to regenerate a random number and the process continues as normal. If multiple collisions occur, this process repeats itself until all tags are successfully read. The designer can select the maximum value of the random number generator so long as the random number is always 16 bits long. The range is set by selecting an integer value Q where the random number generator has a range of 0 to 2Q-1. Holding the number of tags in a system constant, increasing Q decreases the chances of collision but increases the number of query/decrement interrogator transmissions that yield no tag transmission, resulting in a waste of power, time, and information.

Example System:

“Let’s consider a small system (5 tags) and let Q take the value of 6; the system will have a count of 26 – 1 = 63, giving 5 tags a 0.15 probability of collision. At best (no collisions), this will require 69 transmissions from the interrogator. Yet there is a 15% chance a collision will occur; implying that 15% of the time the process will be restarted and the total reader transmission count will be dramatically increased, further reducing the power efficiency and increasing delay” [2].

-

Previous Work and Literature Review

2.1 CDMA RFID

Much of the previous research into CDMA-based RFID has been focused around semi-passive and active RFID tags or has been focused on the use of DSSS itself in RFID tags but did not evaluate the power efficiency of the interrogator. The majority of the research also did not make attempts to preserve the structure and size parameters of the Class-1 Generation-2 standard [3-7].

In May of 2016, Dr. Harold Stern, Cody Lovejoy, Kyle Jones, and I published a 4-page introductory paper (referred to as a set of ‘Notes’) in IEEE International Conference on RFID 2016 titled “A CDMA-based RFID Inventory System” exploring the advantages and disadvantages to the interrogator of using CDMA while attempting to preserve as much of the Class-1 Generation-2 RFID tag structure as possible. Our findings were that there would be a significant decrease in number of required interrogator transmissions (for a small system in which the full EPC memory bank was not necessary in TDMA). We also confirmed that the use of CDMA would not only significantly increase the robustness of the system in a very high noise environment but would also vastly increase the security of the system because without access to the spreading codes, an attacker would have no ability to extract the tag data. Due to the nature of DSSS in CDMA, the tag transmissions may also become indistinguishable from noise to anyone without the proper de-spreading codes.

All the results of this paper were found using MATLAB simulation, hardware simulation and pen-and-paper mathematics. We attempted to design and build our own UHF RFID tags, which proved to be prohibitively expensive. We then attempted to purchase reprogrammable tags from RFID tag manufacturers which proved to be fruitless. Thus, we were unable to physically build the system, which is what we had initially set out to do. My current research is focused on optimizing the Slotted ALOHA protocol by integrating CDMA to allow for multiple tags to be read within each time slot.

2.2 RFID Research Tools

Currently, there exist very few true RFID Research tools. Many RFID manufacturers, such as Alien Technology, sell RFID “Developer Kits”, which allow for little to no modification of aspects of the system that we needed for our research (i.e. transmission rate, multiplexing protocol, tag data storage protocols, frequency hopping options, etc.). Educational companies like Adafruit and Sparkfun sell more flexible RFID development tools but none in the UHF spectrum that are flexible enough for our purposes.

Currently, the most modular RFID system option is the use of a full duplex SDR (such as the National Instruments USRP series of devices) and a MCU-based Wireless Identification Sensing Platform (or WISP) RFID tag developed by The University of Washington and Intel. While this would be a useful tool for our earlier research, the nature of the WISP tags being MCU-based does not give us the modularity necessary for the research proposed here. WISP tags also cost several hundred dollars, making it extremely expensive to test a system with even just one tag.

-

Problem Statement

The problems addressed in the proposed research are twofold: a proper evaluation of integrating CDMA into the Slotted ALOHA protocol on an architectural level and the development of the necessary research tools to do so.

3.1 Integration of CDMA into Slotted ALOHA

While there has been research in the use of CDMA in RFID, as referenced above, there is a gap on the topic of comparing different implementations of CDMA.

The research proposed here will include a full evaluation of the possible integrations of CDMA into the current Class-1 Generation-2 Slotted ALOHA protocol. This will include location of spreading code generation, location of spreading code storage in tag/interrogator memory, number of tags read per slot, and modifications to RFID tag IC architecture to handle additional features. The list of implementations may increase as research is conducted but will all focus on designing for the next generation of RFID tags.

3.2 Research Tool Design

To achieve the necessary modularity at the tag IC architecture level to enact and test these modifications on a hardware level, the clear choice is to use an FPGA. The proposed tool will be an FPGA-based RFID tag that can communicate with other systems using the same protocols as Class-1 Generation-2 passive UHF RFID tags. This tool will be created using building blocks that exist in the literature to create a modular state machine that responds to an input according to the bitrate, memory size and structure, and modulation type as currently outlined in the standard. The tool will only be developed to the degree necessary for this thesis but the work outlined in it will create a framework for future possibilities of low cost RFID tag research tools.

-

Final Deliverables

4.1 Goals and Test Plan

The first goal of this thesis is to have a fully functional HDL software simulation of an RFID IC demonstrating and comparing several different implementations of CDMA capabilities into its architecture to determine optimization for different applications. In this simulation, the specific instructions necessary for CDMA multiplexing will be implemented (without interfering with the Class-1 Generation-2 instruction set), the hardware support for CDMA will be implemented, and the system will conform to the carrier frequency, bitrate, and bandwidth of the Class-1 Generation-2 EPC RFID standard.

The second goal will be a hardware implementation of the IC architecture on an FPGA. This implementation will include the constraints from the simulation. The FPGA implementation will be tested as a wired communication system. Successful demonstration will include an FPGA with the HDL code loaded onto it, test hardware to show that all necessary CDMA commands are functional, and tests that emulate collision to demonstrate how the new IC architecture will handle such problems.

The final goal will be a MATLAB/Simulink simulation to compare the various implementations of CDMA integrated into a TDM Slotted ALOHA multi-tag system.

4.2 Stretch Goals

This thesis contains two stretch goals.

The first stretch goal is a fully functional wireless demonstration of the system. This will contain an SDR-based RFID interrogator, an analog front end connected to the FPGA implementation from the main goal section, an arbitrary waveform generator to emulate the effects of noise/interference, an implementation of the full Class-1 Generation-2 instruction set, and an implementation of hardware and control functions to allow the IC to switch between various protocols, including the current exclusively TDM ALOHA multiplexing protocol.

The final stretch goal is a fully functional CDMA-based RFID IC. The HDL code from the above sections will be implemented in a manufactured wafer and placed into an IC package to be used in an RFID tag complete with a printed antenna.

-

Tools

5.1 Software Tools

- MATLAB

- Simulink

- Vivado (Xilinx)

- Icarus Verilog

- GNURadio

- LabView

- LabView FPGA

5.2 Hardware Tools

- HackRF

- Spectrum Analyzer, Oscilloscope, AWG

- NI MyRio (ARM Cortex A9 and ZYNQ FPGA)

- High Performance FPGA

-

Tentative Schedule

End of 3/17

- Background and introductory sections of Thesis complete

- Block diagram of potential architectures completed and beginning of simulation testing

- Multi-tag system simulation environmental conditions determined and beginning to be implemented

End of 4/17

- Memory blocks and parts of digital control block in IC design software complete

- Additional Instructions are being determined

- Multi-tag system simulation is functional

- Test system design beginning

End of 5/17

- List of instructions complete and control logic is being constructed

- I/O construction beginning

- Multi-tag system simulation is updated to allow for user inputted environment changes.

- Test System Design continuing

- Writing on preliminary results and test system beginning

- Writing on different CDMA implementations and optimization

End of 6/17

- Building blocks of RFID tag HDL code complete (including instruction handling)

- I/O construction continuing

- Test System Design continuing

- Various implementations of CDMA into HDL code beginning

- Multi-tag system simulation complete

- Writing on different CDMA implementations and optimization

End of 7/17

- I/O construction complete

- Test system design continuing

- At least one implementation of CDMA complete

- Performance tests of implementation begin

- Writing on performance results

End of 8/17

- Test System Design complete

- All CDMA implementations are complete

- Performance tests continuing

- Write on performance results

End of 9/17

- Testing complete

- Performance evaluation complete

- Writing on results

10/17

- Combining all previous writing and finalizing thesis

-

References

[1] EPCGlobal, EPC Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860-960 MHz version 1.1.0, 2005

[2] R.Doany, C. Lovejoy, K. Jones, H. Stern, “A CDMA-based RFID Inventory System”. IEEE International Conference on RFID, 2016

[3] C. Mutti and C. Floerkrmeir, “CDMA-based RFID Systems in Dense Scenarios: Concepts and Challenges.” IEEE International Conference on RFID, 2008

[4] R.Measel, C.S. Lester, X. Yifei, R. Primerano, and M. Kam, “Detection Performance of Spread Spectrum Signatures for Passive, Chipless RFID.” IEEE International Conference on RFID, 2014

[5] H. Deng, “Performance Enhancement of Radio Frequency Identification (RFID) Using Spread Spectrum Technology.” IEEE Antennas and Propagation Society International Symposium

[6] Der-Feng Tseng and Zhi-Chien Lin “An Anti-Collision Algorithm in RFID Systems Based on Interference Cancellation and Tag Set Partitioning.” IEEE Vehicular Technology Conference, Spring 2008

[7] E. Vahedi, R.K. Ward, I.F. Blake, “Performance Analysis of RFID Protocols: CDMA Versus the Standard EPC Generation-2” IEEE Transactions on Automation, 2014

[8] WISP RFID Tags, https://wisp5.wikispaces.com/

7.1 References likely to be included in thesis (but were not directly referenced in proposal):

[1] H.P. Stern and S.A. Mahmoud, Communication Systems: Analysis and Design, Prentice-Hall Inc, 2004

[2] A. Lozano-Nieto, RFID Design Fundamentals and Applications, Taylor and Francis Group LLC, 2011

[3] Hsin-Chin Liu, Xin-Can Guo, “A Passive UHF RFID System with Huffman Sequence Spreading Backscatter Signals” Internet of Things Notes in Computer Science vol 4952

[4] A. Debas, B. Balhara, C.J.P. Gupta, “CDMA based Anti-Collision Deterministic Algorithm for RFID Tags”, International Journal of Recent Trends in Engineering and Technology, Vol. 1, No.1, Nov 2009

[5] Chan-Won Park, Bo-Gwan Kim, “A design verification kit for passive RFID system on a Chip”, ISOCC International SoC Design Conference, 2008

[6] R. Verma, Z. Ali, “A Brief Overview of RFID Tag Design in FPGA”, International Journal of Science and Research, 2013

[7] A. Jones, et al, “An automated, FPGA-based reconfigurable, low-power RFID Tag”, Microprocessors and Microsystems, Vol. 31, Issue 2, 5 June 2007, p.116-134

[8] L. Puricelli, R. Torrel, H.L. Peralta, “FPGA Prototyping and Validation of an EPC Gen 2 RFID Tag”, 28th South Symposium on Microelectronics

[9] B. Degnan “Reverse Engineering a Passive UHF RFID Tag”, IEEE International Conference of RFID, 2016

[10] A. W. G. Schmidt, Embedded Systems Design With Platform FPGAs: Principles and Practices, Morgan Kaufmann, 2010